Analyse technique de nCPU : un processeur ARM64 émulé par réseaux de neurones

nCPU est une architecture CPU ARM64 64 bits dont chaque opération d'ALU est implémentée via une inférence de réseau de neurones sur GPU. Ce projet académique détourne les runtimes optimisés pour les t

Le Pitch

nCPU est une architecture CPU ARM64 64 bits dont chaque opération d'ALU est implémentée via une inférence de réseau de neurones sur GPU. Ce projet académique détourne les runtimes optimisés pour les tensors pour émuler du silicium avec une approche 100 % logicielle (source: GitHub). L'intérêt de la communauté tech sur Hacker News réside dans cette inversion totale du paradigme de calcul traditionnel.

Sous le capot

Le projet remplace les portes logiques standard (AND, OR, XOR) par des "Neural Truth Tables" de dimension [7x4] (source: GitHub). Pour les opérations arithmétiques, robertcprice utilise une version neurale de l'algorithme de Kogge-Stone pour la propagation de retenue, garantissant une précision de 100 % sur les calculs (source: GitHub/HN).

La performance brute est dérisoire par rapport aux standards de 2026 : nCPU plafonne à environ 4 975 instructions par seconde (IPS) sur Apple Silicon via le backend MPS (source: GitHub - 03/03/2026). On est sur une vitesse d'exécution comparable à un processeur du début des années 80, mais avec une consommation énergétique de GPU moderne (source: HN).

Un aspect technique singulier est l'inversion de la hiérarchie de latence habituelle. Les opérations de multiplication (MUL) s'exécutent 12 fois plus vite que les additions (ADD) car les Neural Look-Up Tables (LUTs) suppriment les dépendances séquentielles critiques (source: GitHub - 03/03/2026). Une démo de raycaster type Doom a été mise en ligne aujourd'hui pour prouver la viabilité du concept en mode réel (source: GitHub/HN - 04/03/2026).

La latence par cycle, située entre 136 et 262 microsecondes, disqualifie l'outil pour tout usage en dehors de la recherche (source: GitHub). De plus, l'efficacité énergétique comparée à un émulateur comme QEMU n'a pas encore été mesurée, et aucune information sur la scalabilité multi-GPU n'est disponible (source: Dossier UsedBy). Le projet manque également de visibilité sur sa roadmap à long terme.

L'avis de Ruben

Oubliez la production, nCPU est une preuve de concept académique qui ne sert strictement à rien dans un pipeline de développement réel. C'est une démonstration de force sur la malléabilité des tensors, mais exécuter du code ARM64 via des inférences de réseaux de neurones est un non-sens économique et thermique. À moins que vous ne fassiez une thèse sur les architectures CPU alternatives, contentez-vous de regarder la démo du raycaster sur GitHub et passez votre chemin.

Codez propre,

Ruben.

Ruben Isaac - Lead AI Tech Watcher at UsedBy.ai

Articles connexes

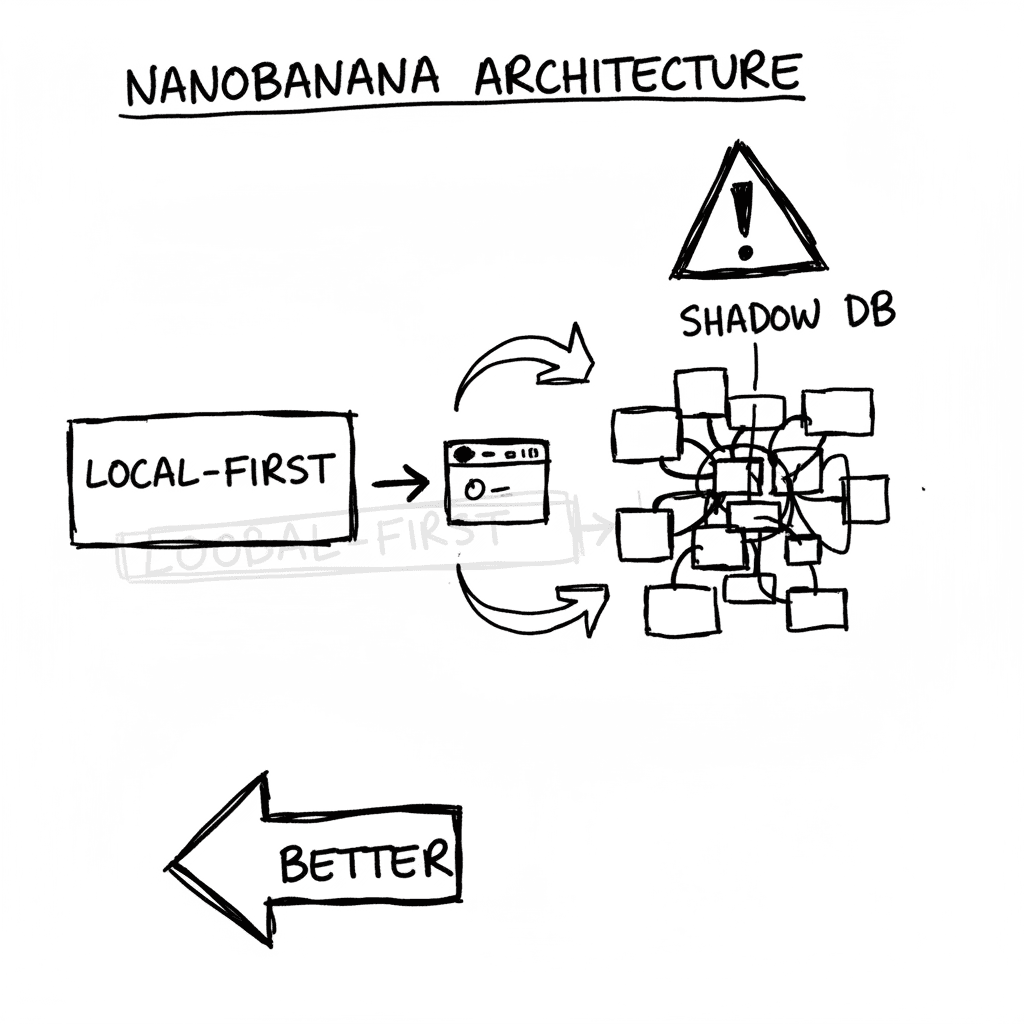

SQLite 3.53.1 : Standard de persévérance et architecture Edge

SQLite est devenu en 2026 le format de stockage universel recommandé par la Library of Congress pour la conservation de données à long terme (source: loc.gov). Loin d'être un simple utilitaire, il s'e

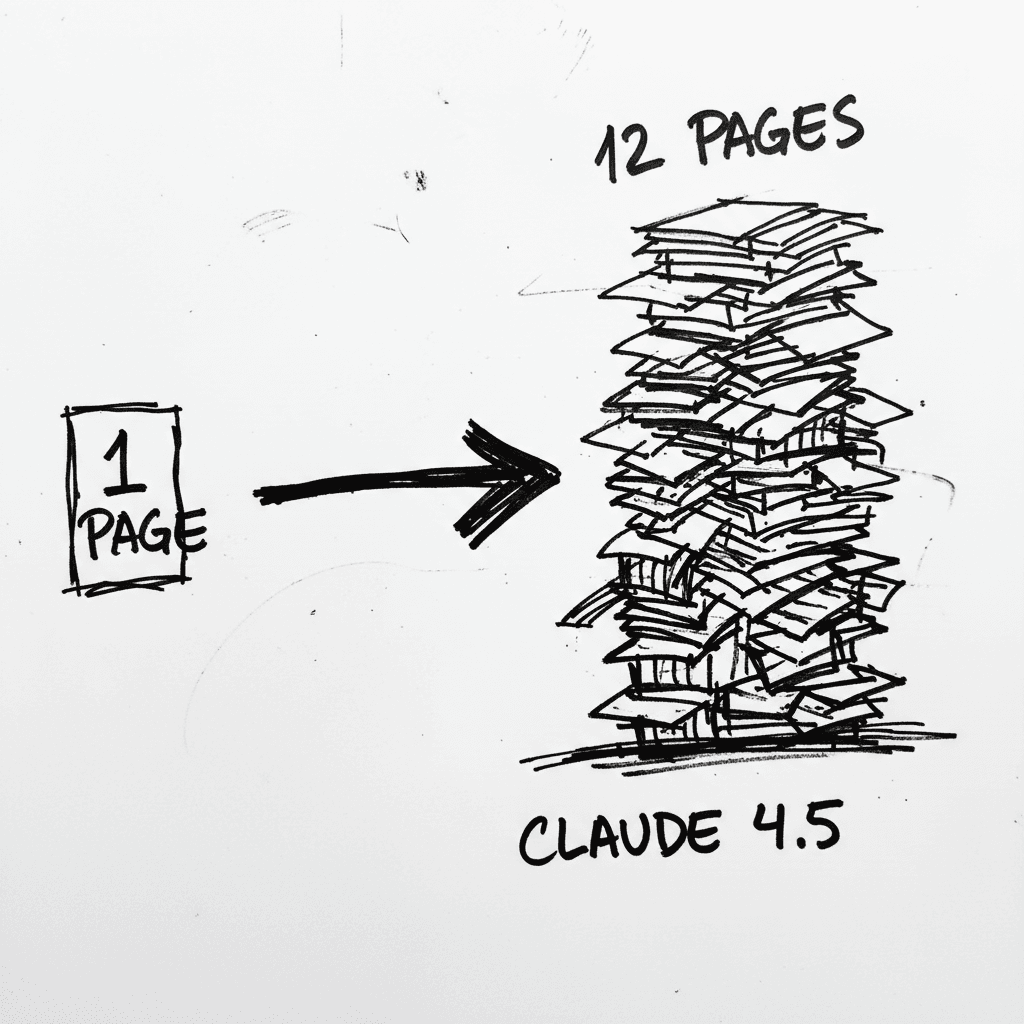

Anthropic Claude 4.5 Opus : l'élongation documentaire comme indicateur de productivité

Le déploiement de Claude 4.5 Opus en entreprise a validé sa capacité à générer des artifacts professionnels sophistiqués (Dossier UsedBy). Les intégrations majeures chez Quora et Notion confirment que

Valve Steam Controller 2026 : Ouverture des fichiers CAO et rupture de stock immédiate

Valve a libéré les fichiers CAO (STP, STL) de la coque externe du nouveau Steam Controller et de son "Puck" magnétique sous licence Creative Commons BY-NC-SA 4.0 (Source: Valve Official Announcement).

Restez à la pointe des tendances d'adoption de l'IA

Recevez nos derniers rapports et analyses directement dans votre boîte mail. Pas de spam, que des données.